1. 위 사진의 밑줄에서 fieldpenetration at the surface region from the drain to the source 가 말하는것이 무엇인가요?

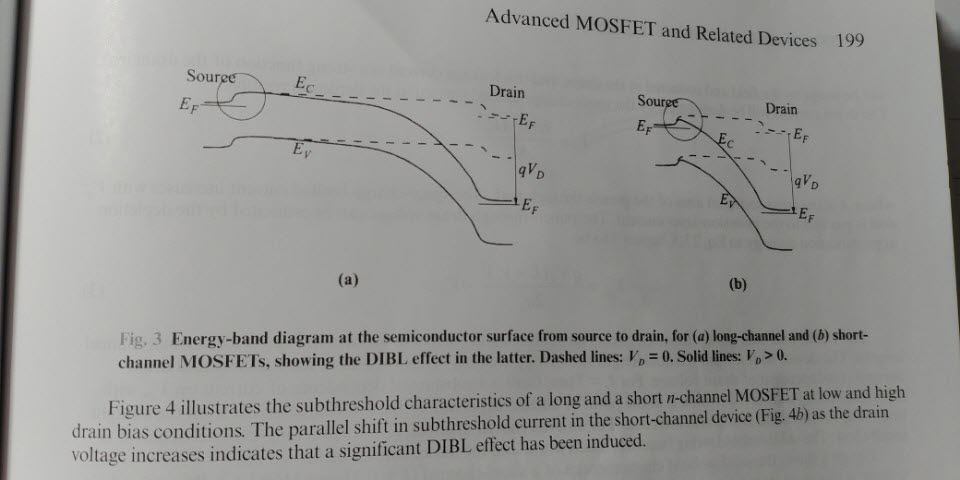

답) DIBL이 일어나는가장 큰 원인은 우선 drain과 source간에 강력한e-field가 걸려야 합니다.

강력한 e-field가 걸리기 위해서는 두가지 조건channel length가 좁거나 Vds가 아주 커져서source와 drain의 에너지 배리어가 낮아져서 것잡을수 없는 전류가 흐르는 현상을 말하는 것이지요. 따라서

“field penetration at the surfaceregion from the drain to the source ”는 강력한 e-field에 의해 source와 drain간에 정상적인 e-field 가 생기는 것 이상으로 전자가 source에서 출발할때 일정 에너지 배리어를 넘어야 하는데 그것조차 penetration 시킬 정도로 에너지 배리어를 낮추게한다는 뜻으로 해석하면 됩니다. DIBL이 언제 생기는지 확실히 알아보려면 Silvaco나 Medici와 같은 반도체 소자 simulation프로그램을 돌려서 각 parameter들을 넣어서DIBL이 생기는 점을 볼수 있습니다. 시뮬레이션시 채널길이와Vds이외에 부수적으로

Semiconductor 농도 그리고 souce/drainwell의 농도등도 약간의 영향을 줄거라 생각이 듭니다.

2. 그리고 저기서 Vth가 낮아지는 이유가 뭔가요?

답) Vth가 낮아진다는뜻은 기본적으로 전류를 잘 흘린다는 뜻이므로 강력한 e-filed(S-D)에 의해 이미 Vgs를 가하지 않은 상태거나 아주 약간의 Vgs를 가한 상태에서도Ids가 흐른다는 얘기이지요.

3. 논문 내용과 관련하여 질문하고 싶다면 논문을 첨부해서 올려도 될까요?

답) 질문의 내용을 보면 고민과 고민끝에 질문한 것인지 아니면 모르는 거면 바로 나한테 물어보는것인지 알수 있습니다. 고민없는 질문은 사절이고 앞으로 정말 고민한 질문만 받도록 하겠습니다. (참고로 위의 질문도 아직 고민의 흔적이 보이지 않지만 처음이자 마지막으로 답을 해줍니다)

주위 동료들에게도 TFT 수강을 권장 부탁합니다.